# ADAPTIVE SOFTWARE DEFINED TERABIT TRANSCEIVER FOR FLEXIBLE OPTICAL Networks

FP7-ICT-GA 318714

SPECIFIC TARGETED RESEARCH PROJECT (STREP) INFORMATION & COMMUNICATION TECHNOLOGIES (ICT)

## Public executive summary of the first Project Periodic Report

D1.7

**Document Type:** Deliverable

**Dissemination Level:** PU<sup>1</sup>

Lead Beneficiary: AIT

Contact Person: Marianna Angelou

(email: mangelou@optronics.gr)

Delivery Due Date: 31/03/2014

Submission date: 10/07/2014

Contributing institutes: All beneficiaries

Authors: ALL

Reviewers: All beneficiaries

<sup>&</sup>lt;sup>1</sup> PU = Public

PP = Restricted to other programme participants (including the Commission Services)

RE = Restricted to a group specified by the consortium (including the Commission Services)

CO = Confidential, only for members of the consortium (including the Commission Services)

## **Adaptive Software Defined Terabit Transceiver For Flexible Optical Networks**

#### At A Glance

#### **Project Website**

#### www.ict-astron.eu

#### **Project Coordinator**

George Papastergiou

Tel: +30 210 9837121

Fax: +30 210 9834814

gpapastergiou@optronics.gr

OPTRONICS TECHNOLOGIES SA

79-81 Thessalonikis str.

18346 Moschato, Greece

Duration: October, 2012-September,

2015

Call Identifier: FP7-ICT-2011-8

Objective: 3.5

Funding Scheme: CP

Total Cost: € 4.2m

EC Contribution: € 3.2m

Project Partners

- OPTRONICS TECHNOLOGIES SA (OPTRONICS), EL

- FINISAR ISRAEL LTD (FINISAR), IL

- FRAUNHOFER-GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG E.V (HHI), DE

- RESEARCH AND EDUCATION LABORATORY IN INFORMATION TECHNOLOGIES (AIT), EL

- UNIVERSITY COLLEGE LONDON (UCL), UK

- UNIVERSITA DEGLI STUDI ROMA TRE (RM3), IT

- ALBIS OPTOELECTRONICS AG (ALBIS), CH

- AIFOTEC AG (AIFOTEC)

- ERICSSON TELECOMUNICAZIONI (TEI), IT

- NATIONAL INSTITUTE OF INFORMATION AND COMMUNICATIONS TECHNOLOGY (NICT), JP

- OPTOSCRIBE LTD (OPTOSCRIBE), UK

- TECHNION ISRAEL INSTITUTE OF TECHNOLOGY (TECHNION), IL

#### **Vision and Aim**

ASTRON project aims at the design and development of an integrated optical transceiver (Tx/Rx) that will enable the wide and cost-efficient deployment of flexible core and access networks.

The main features of the Tx/Rx will be the following:

- Reconfigurable bandwidth allocation using either Optical OFDM or Nyquist WDM technology

- Programmable modulation formats

- Programmable data rate

- Programmable FEC (offering tunability of the ratio of the actual payload to the FEC)

- Energy-efficiency by incorporating state-of-art digital, analog, mixed-signal and optical components into an integrated platform

- Design for Manufacturability using components that can be easily produced at low cost embedded into a compatible package

The implementation of such a system will provide a low-power and low-cost alternative to the use of expensive and power hungry transceivers made from discrete components. The transmitter and receiver modules will be packaged into a small form factor module in order to be compatible with the current network devices. During the ASTRON project the design and the development of compact and scalable photonic integrated components as well as all the necessary electronic circuits and state of the art algorithms to drive and control the optical devices will be realized. These devices will be capable of generating and receiving advanced-modulation-formats (QPSK, 16 QAM) encoded optical signals for high capacity (beyond 1Tb/s) networks. The unique features of the ASTRON architecture allow the transmitter to dynamically support different transmission technologies (optical OFDM or Nyquist WDM) and due to the advanced software-defined signal processing, the proposed system will support different data rates providing flexibility and efficiency.

#### **Main Objectives**

- 1. Design and fabrication of all optical IDFT/DFT AWG-based structures

- a. The basic device will have 8 inputs and output ports and FSR=200 GHz, but a possible upgrade towards 16 channels and the same FSR will be also investigated.

- b. This device will be monolithically integrated on silica planar motherboard in combination with a silica optical power splitter with a 1x8 configuration (with a possible upgrade towards 16 outputs).

- 2. Development and fabrication of InP-based quad IQ Mach-Zehnder Modulator chips

- a. Monolithic InP-based 1.55  $\mu$ m quad-IQ Mach-Zehnder Modulator Photonic Integrated Circuits (PIC) will be designed and fabricated in ASTRON for hybrid assembly onto novel planar optical Silica transmitter boards.

- b. To fabricate the fully integrated planar transmitter board and achieve the target maximum device throughput of 1.12 Tb/s, two quadruple-IQ PICs will be assembled.

- 3. Design and development of integrated multi-channel transmitter module

- a. The fully integrated transmitter will consist of the active InP IQ chips and the passive 1x8 optical power splitter and the 8x8 AWG structure (enabling hte iDFT functionality).

- b. The electrical DC/RF chip-to-board connections as well as the routing of the resulting large number of electrical DC/RF tracks on the optical board will be addressed in order to achieve the specified aggregate terabit transmitter capacity.

- 4. Design and development of integrated optical coherent receiver module

- a. The ASTRON Rx module consists of an 8x8 AWG-based waveguide structure with DFT functionality, optical 90° hybrids, 25 GHz RF traces as well as supporting structures for hybridisation to high speed (≥25 GHz) balanced photodetector arrays.

- b. All the optical and electrical functions will be integrated into/onto a single silica waveguide motherboard.

- 5. Development of advanced hybrid integration platform

- a. the passive and InP active elements developed will be used as the building blocks of the hybrid integration platform

- 6. Development of novel software defined Signal Processing modules and DSP techniques

- a. Software defined signal processing modules will enable the transceiver to be flexible in terms of modulation format, bit rates and bandwidth allocation

- b. DSP techniques will be developed for the electronic mitigation of impairments

### 7. Performance evaluation of the ASTRON transceiver in a terabit-capacity optical testbed

#### **Technical Approach and Achievements**

The implementation technology is based on the combination of InP monolithic elements and silica planar lightwave circuits for achieving cost-effectiveness, high yield, small footprint, low power consumption and device scaling. The ASTRON photonic integration platform will use a "monolithic-on-hybrid" technology in order to integrate different photonic elements such as modulators and photodetectors to form a complete transmitter-receiver system. The photonic transmitting subsystem is composed of an optical Arrayed Waveguide Grating (AWG)-based planar device that optically implements the Inverse Discrete Fourier Transform (IDFT), hybrid integrated with InP-based In Phase-Quadrature (IQ) modulators arrays and a passive optical power splitter. In order to have OFDM or Nyquist WDM data flow, the necessary adaptation is possible to be implemented in the Radio Frequency (RF) domain. In this way the switching between the two technologies depends on the driving conditions of the IQ-modulators.

Figure 1: Architecture of the adaptive software defined optical transceiver

The beneficiaries that form the core of the technology development within **ASTRON** are HHI, ALBIS, AIFOTEC, OPTOSCRIBE and FINISAR. In more detail, HHI will fabricate InP monolithic quad IQ-MZM and will carry out research for developing high-yield monolithic modulator arrays. On the other hand. ALBIS will research and fabricate new generation of photodiodes which are used as "add-ons" in the hybrid integration platform. AIFOTEC will be responsible flip-chipping monolithic chips developed in the frames of the project. HHI and FINISAR will perform RF modelling to extend the electrical interconnection speed to the photonic devices and within the module package.

The receiver subsystem consists of a similar AWG structure that implements the Discrete Fourier Transform (DFT) in order to decode the incoming signals and an array of 90° hybrids followed by balanced Photo-Detectors (PD). The Indium Phosphide (InP) elements enable the generation, modulation and detection of 200 Gsymbol/s optical signals and will be assembled onto the passive optical silica motherboards.

The optical silica motherboards do not carry only the IDFT and DFT waveguide structures, optical splitters and 90° hybrids, but also electrical co-planar High Frequency (HF) transmission lines.

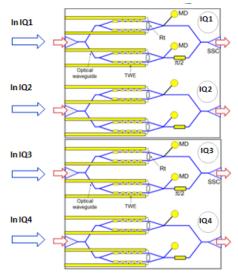

Figure 2: Schematic of the SSC-integrated and flipchip ready quad-IQ MZ modulator PIC as basic active building block in the optical transmitter board. (TWE: Periodically capacity-loaded travelling wave electrode, SSC: spot size converter,

Rt: RF terminating resistor, MD: GalnAs monitor photodiode).

The fabrication process of ASTRON photonic devices is completed with the **development of more advanced planar lightwave circuits with passive structures** (iDFT/DFT, 90° hybrids, optical power splitters) on silica motherboard by OPTOSCRIBE.

RM3, AIT, OPTRONICS and TECHNION will support this technology development by developing modelling and simulation tools to effectively simulate the design and fabrication of the ASTRON devices. Moreover AIT in close cooperation with UCL and TECHNION will develop all the electronic circuits, necessary to drive and control the developed optical modules. FINISAR brings to the group its industrial perspective and experience on such devices fabrication, ensuring that the processes developed and materials chosen are scalable to volume production and sensible from an environmental standpoint.

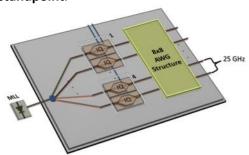

Figure 3: Schematic of of the novel integrated multi-channel terabit capacity transmitter board

At each testing phase, ASTRON prototypes will be delivered to the consortium corresponding beneficiaries for performing necessary characterization tests, after pigtailing and packaging done by OPTOSCRIBE, AIFOTEC and FINISAR. Performance characterization of the fabricated devices on a subsystem-level is carried out in each iteration by FINISAR, UCL, AIT, RM3 and TEI, which are top institutes in the field of optical fibre communications. Through this work,

these beneficiaries will provide experimental feedback to the design and fabrication stages and work in close collaboration with the respective beneficiaries. During the final stages of the project, FINISAR, UCL, AIT, RM3, TEI and TECHNION will join resources in order to combine all the ASTRON devices and assess their system-level performance in advanced test-beds and transmission environments.

The point of view of a system and component vendor is continuously present throughout the duration of the project by TEI and FINISAR respectively so as to steer the activity technology exploitation of ASTRON and provide critical inputs on this. In collaboration with AIT, TEI and FINISAR will carry out techno-economic analyses and market driver studies in order to build a solid base for the commercialisation of the devices that will be exploited after the completion of the project. TEI and FINISAR will also provide appropriate studies to define the required cost/performance relationship of the ASTRON devices necessary, guaranteeing that ASTRON devices will generate significant market interest and be competitive in the photonic components market. Once the **ASTRON** devices have achieved performance that warrants commercial evaluation, network performance of the devices will be evaluated from NICT using its high class test-beds and the Japanese national photonic network JGN-X.

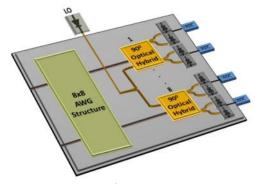

Figure 4: Schematic of the novel integrated multichannel terabit capacity receiver board

The project activities throughout the first reporting period were dedicated to **two main axes** demonstrating fine progress and yielding prolific results both at the **fabrication of the ASTRON devices** as well as the **definition of the system architecture**.

#### Achievements and Progress Beyond the State of the Art

- Extensive system level simulations and experiments were performed pursuing ASTRON transmitter and receiver different configurations and using ASTRON integrated photonics components as main building blocks. Results demonstrate spectral efficiency and transmission distances that match the ASTRON requirements.

- A 3-dimensional AWG was designed and fabricated which produced a super-channel with the required 25 GHz carrier spacing and 200 GHz FSR.

- Design and fabrication of flip-chip ready and SSC-integrated InP test chips consisting of passive planar waveguides and electrical RF transmission lines.

- Development of AuSn bump pad deposition onto optical glass substrates for hybrid chip assembly and electrical chip-to-board connections by utilizing flip-chip bonding technique. Melting and bonding tests were carried out with InP and glass samples.

- Development of a novel etching process on glass substrates for optical Tx board fabrication.

- Simulation and design of electrical RF transmission lines on board and chip level.

- Development and fabrication of single InP-based MZM and IQ MZM with integrated GaInAs monitor photodiodes needed for IQ MZM bias point settings in the ASTRON transmitter.

- First prototype samples of the balanced photodiode arrays were manufactured and tested.

- The design of the Rx test board mask set was finalized and fabrication and processing of the test board wafer has started.

- Waveguide structures on the silica motherboard via mask-less 3D ultrafast laser inscription designed and fabricated; Cascaded 1x2 Y-Splitters were used to produce a passive 1x8 power splitter with 0.2 dB excess loss per junction and output power uniformity of 0.8 dB.

- Developed, implemented and tested the DSP algorithms to realize Nyquist-spaced WDM based on single-carrier dual polarization QAM.

- The full chain of receiver DSP algorithms was developed for the DFT-Spread OFDM filter-bank based sub-banded system (SB DFT-S OFDM).

- Towards the implementation of the reconfigurable FEC module, Quasi-Cyclic LDPC encoder has been developed for the ASTRON transceiver providing high throughput and low latency.

Besides the technical achievements, the business drivers and market revenue forecasts for the ASTRON transceiver were analysed. The project results have been disseminated with publications in high-impact journals and the most relevant conferences.

#### **Expected Impact**

The ASTRON architecture relies on leading edge technology providing important contributions beyond the state-of-the-art with respect to photonic technologies, yet it also provides a favourable ground for future technologies on the future network as a whole. The ASTRON consortium aspires to contribute to communications networks by increasing the transparency, the information throughput, and the power consumption reduction in adaptive Tb/s networks. In addition to the inherent technological benefits, designing and developing compact and scalable adaptive software-defined transceivers will provide telecom operators with the cost-effectiveness required to ensure rapid uptake by the industry. In such

context, the ASTRON Tx/Rx module assumes a role as a key enabler for the next generation infrastructures. Besides, the project provides the complete path to turn its innovative research into a high-value photonic integrated product, reinforcing EU's position in the field. The great involvement of industry in the consortium gives a good insight into the marketing leverage and industrialisation potential of ASTRON. In addition ASTRON is committed to foster technology transfer by encompassing 4 SMEs in its consortium and disseminate knowledge with the involvement of young researchers/students in the teams of the academic partners. Finally, the mutually beneficial cooperation with a leading Japanese research organisation will allow exposure and promotion of the project results also outside the European terrain.